# **SONET Transport**

The terms "Unidirectional Path Switched Ring" and "UPSR" may appear in Cisco literature. These terms do not refer to using Cisco ONS 15xxx products in a unidirectional path switched ring configuration. Rather, these terms, as well as "Path Protected Mesh Network" and "PPMN," refer generally to Cisco's path protection feature, which may be used in any topological network configuration. Cisco does not recommend using its path protection feature in any particular topological network configuration.

This chapter contains specific information about Synchronous Optical Network (SONET) line rates, signal format, overhead functions, and payload mappings for the Cisco ONS 15454. For an introduction to SONET, see the SONET primer in Appendix B. For information about Telcordia's generic requirements for SONET, see GR-253-CORE.

The following topics are covered in this chapter:

- Rates and Formats, page 2-2

- Overhead Mapping, page 2-7

- Data Communications Channel (DCC) Operations, page 2-10

- K3 Byte Remapping, page 2-14

- J1 and J2 Path Trace, page 2-15

- Payload Mapping, page 2-17

- Cross-Connects, page 2-25

- Synchronization and Timing, page 2-60

- Protection Switching, page 2-61

- Network Topologies, page 2-74

- Inservice Topology Conversions, page 2-96

- SONET Span Upgrades, page 2-98

### **Rates and Formats**

Inside the ONS 15454, STS-N connections may be allowed that do not correspond to the standard signal definitions. For example, Ethernet card connections in the ONS 15454 may be made with the standard signals and also STS-6C and STS-24C line rates, because the STS-6C and STS-24C signals are carried within standard SONET links and never appear outside of the ONS 15454 system. Table 2-1 lists the SONET line rates supported by the ONS 15454.

Table 2-1 Supported SONET Line Rates

| STS-N Electrical Level | Optical Carrier (OC-N)<br>Level | Line Rate (Mb/s) | Hierarchical<br>Relationship |

|------------------------|---------------------------------|------------------|------------------------------|

| STS-1                  | OC-1                            | 51.840           | Standard                     |

| STS-3                  | OC-3                            | 155.52           | 3 times STS-1                |

| STS-12                 | OC-12                           | 622.08           | 4 times STS-3                |

| STS-48                 | OC-48                           | 2,488.32         | 4 times STS-12               |

| STS-192                | OC-192                          | 9,953.28         | 4 times STS-48               |

#### **STS Concatenation**

In the ONS 15454, valid concatenated payloads exist from STS-1 to STS-192c and are carried in the optical OC-N signal or STS-N electrical signal. Valid STS-Nc payloads for the ONS 15454 are listed in Table 2-2.

Table 2-2 Supported Concatenated Bandwidth Sizes

| Payload Bandwidth (Mb/s) | Inside or Outside the ONS 15454<br>Network                        |

|--------------------------|-------------------------------------------------------------------|

| 49.536                   | Both                                                              |

| 148.608                  | Both                                                              |

| 297.216                  | Inside Only                                                       |

| 594.432                  | Both                                                              |

| 1,188,864                | Both                                                              |

| 2,377.728                | Both                                                              |

| 9,510.912                | Both                                                              |

|                          | 49.536<br>148.608<br>297.216<br>594.432<br>1,188,864<br>2,377.728 |

When STS-1's are concatenated, the path overhead in the first STS-1 controls the payload. Path overhead in the remaining STS-1's is still carried, but it is not used.

#### **Concatenated STS Time Slot Assignments**

Table 2-3 shows the available time slot assignments for concatenated STSs when using CTC to provision circuits.

Table 2-3 STS Mapping Using CTC

| Starting STS | STS-3c | STS-6c | STS-9c | STS-12c | STS-24c | STS-48c |

|--------------|--------|--------|--------|---------|---------|---------|

| 1            | Yes    | Yes    | Yes    | Yes     | Yes     | Yes     |

| 4            | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 7            | Yes    | Yes    | No     | No      | Yes     | No      |

| 10           | Yes    | No     | Yes    | No      | Yes     | No      |

| 13           | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 16           | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 19           | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 22           | Yes    | No     | No     | No      | Yes     | No      |

| 25           | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 28           | Yes    | Yes    | Yes    | No      | No      | No      |

| 31           | Yes    | Yes    | Yes    | No      | No      | No      |

| 34           | Yes    | No     | Yes    | No      | No      | No      |

| 37           | Yes    | Yes    | Yes    | Yes     | No      | No      |

| 40           | Yes    | Yes    | Yes    | No      | No      | No      |

| 43           | Yes    | Yes    | Yes    | No      | No      | No      |

| 46           | Yes    | No     | Yes    | No      | No      | No      |

| 49           | Yes    | Yes    | Yes    | Yes     | Yes     | Yes     |

| 52           | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 55           | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 58           | Yes    | No     | Yes    | No      | Yes     | No      |

| 61           | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 64           | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 67           | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 70           | Yes    | No     | Yes    | No      | Yes     | No      |

| 73           | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 76           | Yes    | Yes    | Yes    | No      | No      | No      |

| 79           | Yes    | Yes    | Yes    | No      | No      | No      |

| 82           | Yes    | No     | Yes    | No      | No      | No      |

| 85           | Yes    | Yes    | Yes    | Yes     | No      | No      |

| 88           | Yes    | Yes    | Yes    | No      | No      | No      |

| 91           | Yes    | Yes    | Yes    | No      | No      | No      |

| 94           | Yes    | No     | Yes    | No      | No      | No      |

| 97           | Yes    | Yes    | Yes    | Yes     | Yes     | Yes     |

| 100          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 103          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 106          | Yes    | No     | Yes    | No      | Yes     | No      |

Table 2-3 STS Mapping Using CTC (continued)

| Starting STS | STS-3c | STS-6c | STS-9c | STS-12c | STS-24c | STS-48c |

|--------------|--------|--------|--------|---------|---------|---------|

| 109          | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 112          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 115          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 118          | Yes    | No     | Yes    | No      | Yes     | No      |

| 121          | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 124          | Yes    | Yes    | Yes    | No      | No      | No      |

| 127          | Yes    | Yes    | Yes    | No      | No      | No      |

| 130          | Yes    | No     | Yes    | No      | No      | No      |

| 133          | Yes    | Yes    | Yes    | Yes     | No      | No      |

| 136          | Yes    | Yes    | Yes    | No      | No      | No      |

| 139          | Yes    | Yes    | Yes    | No      | No      | No      |

| 142          | Yes    | No     | Yes    | No      | No      | No      |

| 145          | Yes    | Yes    | Yes    | Yes     | Yes     | Yes     |

| 148          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 151          | Yes    | Yes    | No     | No      | Yes     | No      |

| 154          | Yes    | No     | Yes    | No      | Yes     | No      |

| 157          | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 160          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 163          | Yes    | Yes    | Yes    | No      | Yes     | No      |

| 166          | Yes    | No     | No     | No      | Yes     | No      |

| 169          | Yes    | Yes    | Yes    | Yes     | Yes     | No      |

| 172          | Yes    | Yes    | Yes    | No      | No      | No      |

| 175          | Yes    | Yes    | No     | No      | No      | No      |

| 178          | Yes    | No     | No     | No      | No      | No      |

| 181          | Yes    | Yes    | Yes    | Yes     | No      | No      |

| 184          | Yes    | Yes    | Yes    | No      | No      | No      |

| 187          | Yes    | Yes    | No     | No      | No      | No      |

| 190          | Yes    | No     | No     | No      | No      | No      |

#### **VT Structure**

Signals with bit rates less than DS3 at 45 Mb/s can be carried in the ONS 15454 by mapping these lower rate signals into sections of an STS-1 frame. These sections are each called a Virtual Tributary (VT). Each STS-1 frame is divided into exactly seven virtual tributary groups (VTG).

A single STS-1 frame cannot be partially filled with VTGs and use its remaining payload for something else, like ATM cell transport. The STS-1 can either be sectioned off into exactly 7 VTGs or left whole. The 7 VTGs in an STS-1 frame consists of 108 bytes each.

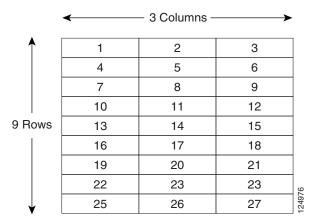

The ONS 15454 system utilizes the Asynchronous VT1.5 structure, which is diagramed in Figure 2-1. Note that there are 27 bytes in the VT1.5. 24 bytes make up the payload of the DS1 signal. The remaining 3 bytes are used for path overhead.

Figure 2-1 VT1.5 Structure

Each STS-1 can support 28 VT1.5 mapped DS1 signals. Table 2-4 illustrates how the ONS 15454 numbers these VT1.5 mapped signals compared to the VT Group numbering scheme defined in Telcordia GR-253-CORE.

Table 2-4 ONS 15454 VT1.5 Numbering Scheme

| DS1 Number | ONS 15454 VT1.5<br>Number | GR-253-CORE VT Group<br>Number | GR-253-CORE VT<br>Number |

|------------|---------------------------|--------------------------------|--------------------------|

| 1          | VT1-1                     | 1                              | 1                        |

| 2          | VT2-1                     | 2                              | 1                        |

| 3          | VT3-1                     | 3                              | 1                        |

| 4          | VT4-1                     | 4                              | 1                        |

| 5          | VT5-1                     | 5                              | 1                        |

| 6          | VT6-1                     | 6                              | 1                        |

| 7          | VT7-1                     | 7                              | 1                        |

| 8          | VT1-2                     | 1                              | 2                        |

| 9          | VT2-2                     | 2                              | 2                        |

| 10         | VT3-2                     | 3                              | 2                        |

| 11         | VT4-2                     | 4                              | 2                        |

| 12         | VT5-2                     | 5                              | 2                        |

| 13         | VT6-2                     | 6                              | 2                        |

| 14         | VT7-2                     | 7                              | 2                        |

| 15         | VT1-3                     | 1                              | 3                        |

| 16         | VT2-3                     | 2                              | 3                        |

| 17         | VT3-3                     | 3                              | 3                        |

| 18         | VT4-3                     | 4                              | 3                        |

Table 2-4 ONS 15454 VT1.5 Numbering Scheme (continued)

| DS1 Number | ONS 15454 VT1.5<br>Number | GR-253-CORE VT Group<br>Number | GR-253-CORE VT<br>Number |

|------------|---------------------------|--------------------------------|--------------------------|

| 19         | VT5-3                     | 5                              | 3                        |

| 20         | VT6-3                     | 6                              | 3                        |

| 21         | VT7-3                     | 7                              | 3                        |

| 22         | VT1-4                     | 1                              | 4                        |

| 23         | VT2-4                     | 2                              | 4                        |

| 24         | VT3-4                     | 3                              | 4                        |

| 25         | VT4-4                     | 4                              | 4                        |

| 26         | VT5-4                     | 5                              | 4                        |

| 27         | VT6-4                     | 6                              | 4                        |

| 28         | VT7-4                     | 7                              | 4                        |

# **M13 Multiplexing**

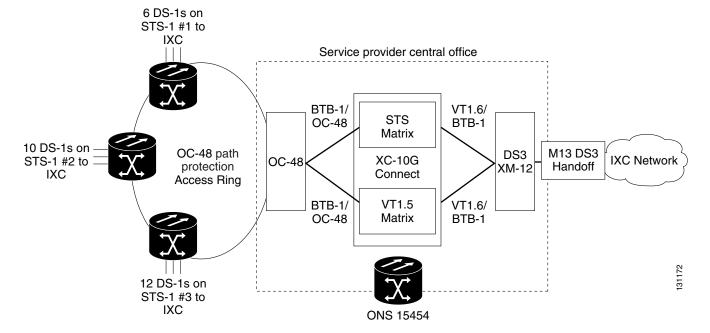

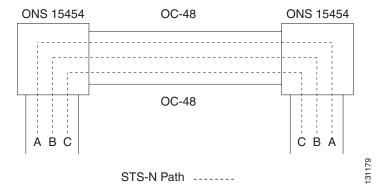

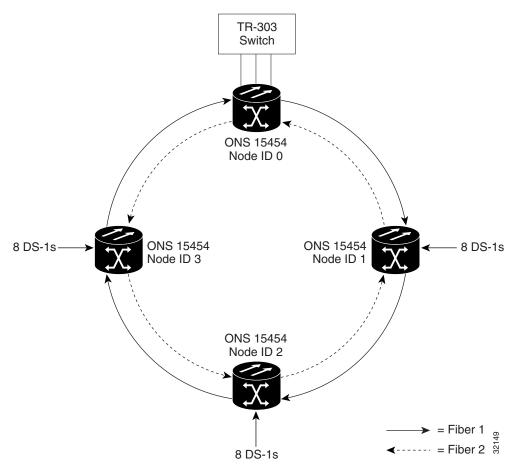

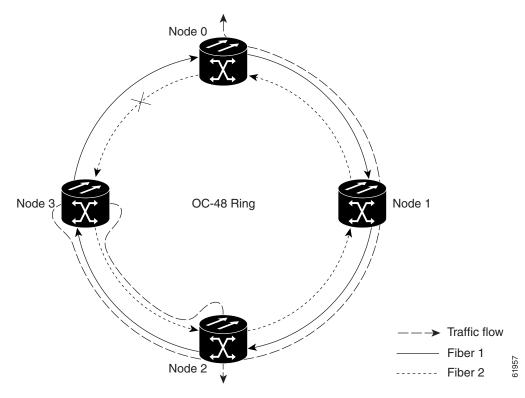

The ONS 15454 provides GR499-CORE compliant M13 multiplexing to groom D1s into channelized DS3 signals. This transmux function is provided by the DS3XM-6 and DS3XM-12 transmux cards. In Figure 2-2, the ONS 15454 is pictured collecting multiple DS1s from IXC customers around the OC-48 path protection access ring and, in the ONS 15454 node at the Service Provider's Central Office, transmitting them within a channalized DS3 signal to the IXC's network.

Figure 2-2 Ported Transmux Function

The DS3XM-6 and DS3XM-12 cards can terminate either C-bit or M13 formatted DS-3 signals and demultiplex them into DS1 signals for transport as VC11/VT1.5 payloads. Each DS3 signal is partitioned into M-frames mapped to 28 DS-1 signals in an M13 multiplex unit. The 28 DS-1 signals are then converted to VT1.5 payloads (1.728 Mb/s) for DS-1 transport.

Conversely, these transmux cards can take 28 T-1s and multiplex them into a channeled C-bit or M13 framed DS3. This is accomplished in two steps. In the first step, 4 DS1 signals are multiplexed to reach a 6.312 Mb/s transmission rate inside the M13 multiplex unit. The M13 unit then multiplexes 7 of the 6.312 Mb/s signals to generate the DS3 output.

With the introduction of the DS3XM-12 card in Release 5.0, the ONS 15454 can support up to 96 DS3 transmux ports in a single shelf.

#### **Portless Transmux Function**

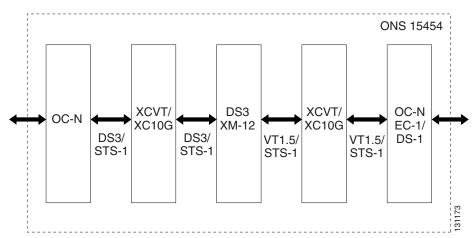

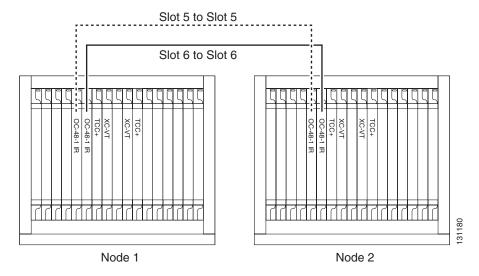

The portless transmux function enables the ONS 15454 to multiplex and demultiplex DS3 signals directly from optical interfaces without requiring an external DS3 card to groom DS1s from DS3 signals inside an STS-1 from an optical port. Only the DS3XM-12 card can provide this function, which is illustrated in Figure 2-3.

Figure 2-3 Portless Transmux Function

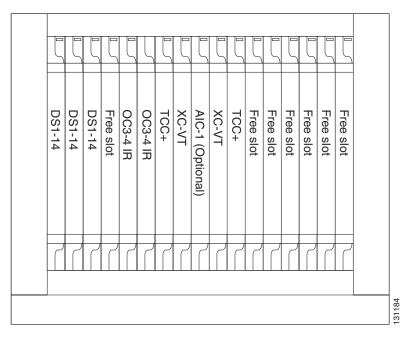

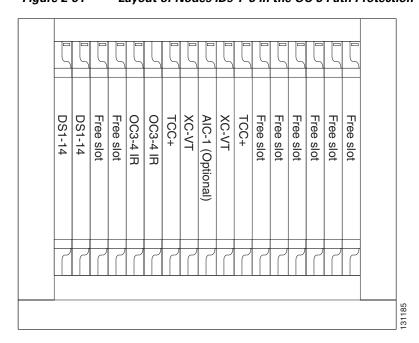

Only the DS3XM-12 card provides portless transmux interfaces that can change transported DS3s within optical interfaces into VT1.5s. Each DS3XM-12 card can provide either 6 or 12 portless transmux interfaces depending on the card's slot position and the type of cross-connect card as follows:

If the DS3XM12 card is in slots 1-4 or 14-17 and the cross-connect is an XC-VT then the backplane bandwidth size is an STS-12, which supports a maximum of 6 portless transmux ports.

If the DS3XM12 card is slots 5-6 or 12-13 and the cross-connect is an XC-VT, or slots 1-6 and 12-17 and cross-connect is an XC-10G the backplane size is an STS-48, which supports a maximum of 12 portless transmux ports.

# **Overhead Mapping**

The individual SONET overhead byte designations are laid out in Table 2-5.

Table 2-5 SONET Transport and Path Overhead Byte Designations

| Transport Overhead |                    |               |                       | Path Overhead            |

|--------------------|--------------------|---------------|-----------------------|--------------------------|

| Section            | Framing            |               | Trace                 | Trace                    |

|                    | A1                 | A2            | J0/Z1                 | J1                       |

|                    | BIP-8              | Orderwire     | User                  | BIP-8                    |

|                    | B1/undefined       | E1/undefined  | F1/undefined          | В3                       |

|                    | <b>Section DCC</b> |               |                       | Signal Label             |

|                    | D1/undefined       | D2/undefined  | D3/undefined          | C2                       |

| Line               | Pointer            | Pointer       | <b>Pointer Action</b> | Path Status              |

|                    | H1                 | H2            | Н3                    | G1                       |

|                    | BIP-8              | APS           | APS                   | <b>User Channel</b>      |

|                    | B2/undefined       | K1/undefined  | K2/undefined          | F2                       |

|                    | Line DCC           |               | Indicator             |                          |

|                    | D4/undefined       | D5/undefined  | D6/undefined          | H4                       |

|                    | Line DCC           |               |                       | Growth                   |

|                    | D7/undefined       | D8/undefined  | D9/undefined          | Z3                       |

|                    | Line DCC           |               |                       | Growth                   |

|                    | D10/undefined      | D11/undefined | D12/undefined         | Z4                       |

|                    | SSM                | REI-L         | Orderwire             | <b>Tandem Connection</b> |

|                    | S1/Z1              | M0 or M1/Z2   | E2/undefined          | Z5                       |

Table 2-6 provides a list of supported and unsupported SONET overhead bytes for the Cisco ONS 15454.

Table 2-6 Supported and Unsupported SONET Overhead Bytes

| SONET Overhead |       |                      | Status        |

|----------------|-------|----------------------|---------------|

| Section        | A1-A2 | Framing              | Supported     |

|                | J0    | Section Trace        | Not Supported |

|                | Z0    | Section Growth       | Supported     |

|                | B1    | Section BIP-8        | Supported     |

|                | E1    | Local Orderwire      | Supported     |

|                | F1    | Section User Channel | Not Supported |

Table 2-6 Supported and Unsupported SONET Overhead Bytes (continued)

| Line     | H –H3       | STS Pointer                        | Supported     |

|----------|-------------|------------------------------------|---------------|

|          | B2          | Line BIP-8                         | Supported     |

|          | K –K2       | APS Channel                        | Supported     |

|          | K2          | Bits 6-8, RDI-L &<br>AIS-L Detect  | Supported     |

|          | D4-D12      | Line DCC                           | Supported     |

|          | S1          | Synch Status<br>Messaging          | Supported     |

|          | M0 – M1     | REI-L                              | Supported     |

|          | E2          | Express Orderwire                  | Supported     |

| STS Path | H1–H3       | STS Pointer                        | Supported     |

|          | H –H2       | AIS-P Detect                       | Supported     |

|          | J1-J2       | STS Path Trace                     | Supported     |

|          | В3          | STS Path BIP-8                     | Supported     |

|          | C2          | STS Path Signal Label              | Supported     |

|          | C2          | PDI-P                              | Supported     |

|          | G1 bits 1–4 | REI-P                              | Supported     |

|          | G1 bits 5–7 | ERDI-P                             | Not Supported |

|          | F2          | Path User Channel                  | Not Supported |

|          | H4          | Multi-Frame Indicator<br>(VT only) | Supported     |

|          | H4          | Other                              | Not Supported |

|          | G1 bits 1–4 | REI-P                              | Supported     |

|          | G1 bits 5–7 | ERDI-P                             | Not Supported |

|          | F2          | Path User Channel                  | Not Supported |

|          | H4          | Multi-Frame Indicator<br>(VT only) | Supported     |

|          | H4          | Other Not                          | Supported     |

|          | Z3          | Growth                             | Not Supported |

|          | F2, H4, Z3  | DQDB Mapping                       | Not Supported |

|          | Z4          | Growth                             | Not Supported |

|          | Z5          | Growth                             | Not Supported |

|          | <b>Z</b> 5  | Tandem Connect<br>Channel          | Not Supported |

|          | V1-V3       | VT Pointer                         | Supported     |

| VT Path | V1-V3        | VT Pointer             | Supported     |

|---------|--------------|------------------------|---------------|

|         | V1-V3        | VT Pointer             | Supported     |

|         | V1-V2        | AIS-V Detect           | Supported     |

|         | V5 bits 1, 2 | VT Path BIP-2          | Supported     |

|         | V5 bit 3     | REI-V                  | Supported     |

|         | V5 bit 4     | FRI-V (byte sync only) | Not Supported |

|         | V5 bits 5–7  | VT Path Signal Label   | Not Supported |

|         | V5 bit 8     | RDI-V                  | Not Supported |

|         | J2           | VT Path Trace          | Not Supported |

|         | Z6           | Growth                 | Not Supported |

|         | Z7 bits 5-7  | ERDI-V                 | Not Supported |

|         | <b>Z</b> 7   | Growth                 | Not Supported |

Table 2-6 Supported and Unsupported SONET Overhead Bytes (continued)

# **Data Communications Channel (DCC) Operations**

SONET provides four data communications channels (DCCs) for network element operation, administration, maintenance, and provisioning: one on the SONET Section layer (D1 to D3 bytes) and three on the SONET Line layer (D4 to D12 bytes). The ONS 15454 uses the Section DCC (SDCC) for ONS 15454 management and provisioning. An SDCC and Line DCC (LDCC) each provide 192 Kb/s of bandwidth per channel. The aggregate bandwidth of the three LDCCs is 576 Kb/s. When multiple DCC channels exist between two neighboring nodes, the ONS 15454 balances traffic over the existing DCC channels using a load balancing algorithm. This algorithm chooses a DCC for packet transport by considering packet size and DCC utilization.

Software Release 4.6 enables existing TCC2/TCC2P-equipped network elements to support 1 Section Data Communications Channel (SDCC) termination per OC-N span and up to 68 data communications channel (DCC) terminations, providing hosting of up to 34 path protection configurations, 5 bi-directional line switched rings (BLSRs), or a combination of the two. This enhancement supports provisionable threshold-crossing-alert (TCA) settings for -48 VDC system input monitoring. With Release 4.0, there can be 1 SDCC termination per OC-N span, with a maximum of 32 DCC terminations per ONS 15454. Previous software releases can support 1 SDCC termination per OC-N span, with a maximum of 10 DCC terminations per ONS 15454.

The SDCC is defined in the first STS-1 of an STS-N frame. SDCC channels need to be terminated via a provisioning session at each ONS 15454 node in the ring before messages can flow between nodes. After the SDCC channels have been terminated, OAM&P will start up automatically within each ONS 15454 node. If there are two ONS 15454 nodes connected by multiple OC-N spans, the SDCC on each of these spans does not have to be terminated at each node to start the flow of OAM&P information. You only need to terminate the SDCCs on the ports of the OC-N cards that are going to serve as the OC-N trunk ports for the ring. SDCCs that are not terminated are available for DCC tunneling.

A SONET link that carries payload from an ONS 15454 node to a third-party's SONET node will also have an SDCC defined in the Section Overhead. However, OAM&P messages will not be recognized by the third-party's node, and the SDCC should not be enabled. Disabling the SDCC will not have any affect on the DS3, DS1, and other payload signals carried between nodes.

### **DCC Tunneling**

Terminated SDCCs used by the ONS 15454 cannot be used as a DCC tunnel end-point, and a SDCC that is used as an DCC tunnel end-point cannot be terminated. All DCC tunnel connections are bi-directional.

You can tunnel the SONET DCC from third party equipment across ONS 15454 networks using one of two tunneling methods, a traditional DCC tunnel or an IP-encapsulated tunnel.

#### **Traditional DCC Tunnels**

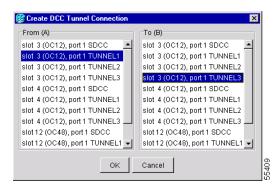

In traditional DCC tunnels, you can use the 3 LDCCs and the SDCC (when not used for ONS 15454 DCC terminations) for a maximum of 4 DCC tunnels. A traditional DCC tunnel endpoint is defined by slot, port, and DCC, where a DCC can be either the section DCC or one of the line DCCs (see Figure 2-4). You can link LDCCs to LDCCs and link SDCCs to SDCCs. You can also link a SDCC to a LDCC, and a LDCC to a SDCC. To create a DCC tunnel, you connect the tunnel endpoints from one ONS 15454 optical port to another. Software Release 4.0 and higher can support a maximum of 84 DCC tunnel connections for each ONS 15454. Table 2-7 shows the DCC tunnels that you can create using different OC-N cards.

Figure 2-4 Selecting DCC Tunnel End-Points

Table 2-7 Allowable DCC Tunnels

| Card                     | DCC  | SONET Layer | Overhead Bytes |

|--------------------------|------|-------------|----------------|

| OC3 IR 4/STM1 SH<br>1310 | DCC1 | Section     | D1 – D3        |

Table 2-7 Allowable DCC Tunnels (continued)

| Card                                    | DCC  | SONET Layer | Overhead Bytes |

|-----------------------------------------|------|-------------|----------------|

| OC3 IR/STM1 SH                          | DCC1 | Section     | D1 – D3        |

| 1310-8; All OC-12,<br>OC-48, and OC-192 | DCC2 | Line        | D4 – D6        |

| cards                                   | DCC3 | Line        | D7 – D9        |

|                                         | DCC4 | Line        | D10 – D12      |

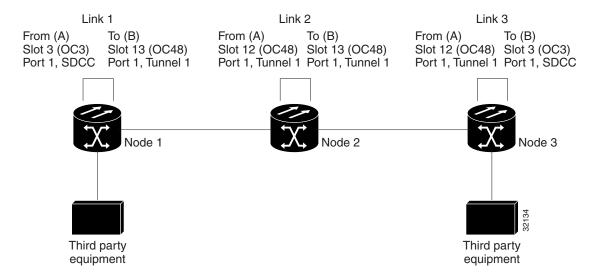

Figure 2-5 shows an example of a DCC tunnel. Third-party equipment is connected to OC-3 cards at Node 1/Slot 3/Port 1 and Node 3/Slot 3/Port 1. OC-48 trunk cards connect each ONS 15454 node. In the example, 3 tunnel connections are created, 1 at Node 1 (OC-3 to OC-48), 1 at Node 2 (OC-48 to OC-48), and 1 at Node 3 (OC-48 to OC-3).

Figure 2-5 DCC Tunnel Example

When you create DCC tunnels, keep the following guidelines in mind:

- Each ONS 15454 can have up to 84 DCC tunnel connections.

- Each ONS 15454 can have up to 84 Section DCC terminations.

- A section DCC that is terminated cannot be used as a DCC tunnel endpoint.

- A section DCC that is used as a DCC tunnel endpoint cannot be terminated.

- All DCC tunnel connections are bi-directional.

#### **IP-Encapsulated Tunnels**

An IP-encapsulated tunnel puts a SDCC in an IP packet at a source node and dynamically routes the packet to a destination node. To compare traditional DCC tunnels with IP-encapsulated tunnels, a traditional DCC tunnel is configured as one dedicated path across a network and does not provide a failure recovery mechanism if the path is down. An IP-encapsulated tunnel is a virtual path, which adds protection when traffic travels between different networks.

IP-encapsulated tunneling has the potential of flooding the DCC network with traffic resulting in a degradation of performance for CTC. The data originating from an IP tunnel can be throttled to a user-specified rate, which is a percentage of the total SDCC bandwidth.

Each ONS 15454 supports up to 10 IP-encapsulated tunnels. You can convert a traditional DCC tunnel to an IP-encapsulated tunnel or an IP-encapsulated tunnel to a traditional DCC tunnel. Only tunnels in the DISCOVERED state can be converted.

Converting from one tunnel type to the other is service-affecting.

# K1 and K2 Byte Switching

The K1 and K2 bytes in the Line Overhead are used for automatic protection switching (APS) commands and error conditions between pieces of SONET node equipment. These two bytes are only used in the first STS-1 of an STS-N signal. The meaning of the K1 and K2 bytes depends on the type of protection used. For example, bits 1-4 of the K1 byte have the following meaning shown in Table 2-8 when a 1+1 fiber protection scheme is used.

Table 2-8 Meaning of K1 Bits 1 to 4

| K1 Bits | Description              |

|---------|--------------------------|

| 1111    | Lockout of Protection    |

| 1101    | SF - High Priority       |

| 1011    | SD - High Priority       |

| 1001    | (not used)               |

| 0111    | (not used)               |

| 0101    | (not used)               |

| 0011    | (not used)               |

| 0001    | Do Not Revert            |

| 1110    | Forced Switch            |

| 1100    | SF - Low Priority        |

| 1010    | SD - Low Priority        |

| 1000    | Manual Switch            |

| 0110    | Wait-to-Restore (Note 3) |

| 0100    | Exercise (Note 4)        |

| 0010    | Reverse Request (Note 5) |

| 0000    | No Request               |

Remember that the SONET overhead is sent with the SONET frame every 125 microseconds between nodes. So if a SONET node detects a fault on the receive bit stream from a node, the receiving node can notify the transmitting node immediately by changing the state of the K1 and K2 bytes. The transmitting node does not have to compose a message and send it through the DCC channels. The node receiving the new K1/K2 state must begin processing the change within three frame receptions (3 times 125

microseconds or 375 microseconds). The ONS 15454 conforms to the GR-253-CORE standard for K1 and K2 state signaling, so other vendor equipment should be interoperable with ONS 15454 transmission payload and protection signaling.

# **K3 Byte Remapping**

Do not perform K3 byte remapping on the Cisco ONS 15454 unless it is required to complete a BLSR that connects to third-party equipment.

The Cisco ONS 15454 uses the undefined K1 byte within STS-2 to improve BLSR switching times. Cisco renamed the K1 byte within STS-2 the K3 byte. The improved switching time allows a Cisco to support the 50ms BLSR switch time in rings with up to 16 ONS 15454 nodes.

If a BLSR is routed through third-party equipment that cannot transparently transport the K3 byte, you can remap it to either the Z2, E2, or F1 bytes on the ONS 15454 OC-48 any slot (AS) cards. K3 byte remapping is not available on other OC-N cards. If you remap the K3 byte, you must remap it to the same byte on each BLSR trunk card that connects to the third-party equipment. All other BLSR trunk cards should remain mapped to the K3 byte.

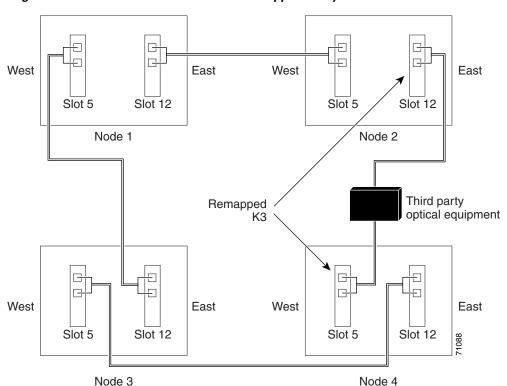

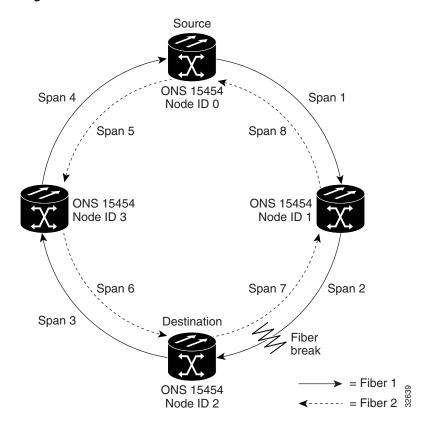

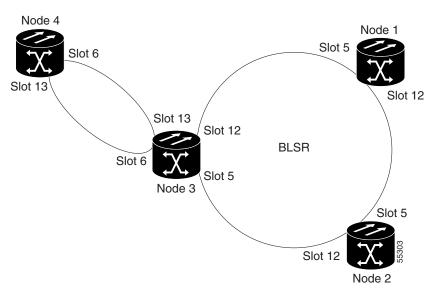

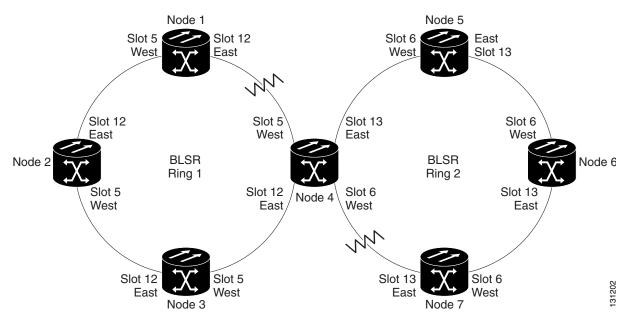

For example, in Figure 2-6, a BLSR span between Node 2 and Node 4 passes through third-party equipment. Because this equipment cannot transparently transport the K3 byte, the OC-48AS card at Node 2/Slot 12 and the OC-48AS card at Node 4/Slot 5 are provisioned to use an alternate byte. Other BLSR trunk cards are not changed.

Figure 2-6 BLSR Provisioned with Remapped K3 Byte

### J1 and J2 Path Trace

The SONET J1 and J2 Path Trace is a repeated, fixed-length string comprised of 64 consecutive J1 bytes. J1 Path Trace can be used to carry a remote hostname, an interface name/number, an IP address, or anything that can be used to uniquely identify a circuit. J1 Path Trace is commonly used to troubleshoot circuit paths through networks. The Cisco ONS 15454 can monitor the J1 Path Trace strings on each STS and compare the received string with the transmitted string. A TIM-P alarm is raised if the string received at a circuit drop port does not match the string the port expects to receive. Two path trace modes are available:

- Automatic—The receiving port assumes the first J1 string it receives as the baseline J1 string.

- Manual—The receiving port uses a string that you manually enter as the baseline J1 string.

Table 2-9 shows the ONS 15454 cards that support J1 Path Trace. DS-1 and DS-3 cards can transmit and receive the J1 field, while the EC-1, OC-3, OC-48AS, and OC-192 can only receive it. A new feature added in System Release 4.0 gives the ONS 15454 the ability to support J1 Path Trace monitoring while a BLSR switch is in effect. Cards not listed in the table do not support the J1 byte. The DS3XM-12 card supports J2 path trace for VT circuits.

Table 2-9 ONS 15454 Cards Supporting J1 Path Trace

| J1 Function                | Cards                                                                       |  |  |  |  |

|----------------------------|-----------------------------------------------------------------------------|--|--|--|--|

| Tramsmit and Receive       | CE-100T-8                                                                   |  |  |  |  |

|                            | DS1-14, DS1N-14                                                             |  |  |  |  |

|                            | DS3-12E, DS3N-12E, DS3XM-6, DS3XM-12, DS3/EC1-48                            |  |  |  |  |

|                            | G1000-4, G1K-4                                                              |  |  |  |  |

|                            | ML100T-12, ML1000-2                                                         |  |  |  |  |

| Receive (Monitor Only)     | EC1-12                                                                      |  |  |  |  |

|                            | OC3 IR 4 1310, OC3/STM1 IR 8 1310                                           |  |  |  |  |

|                            | OC12/STM4-4                                                                 |  |  |  |  |

|                            | OC48 IR/STM16 SH AS 1310,                                                   |  |  |  |  |

|                            | OC48 LR/STM16 LH AS 1550<br>OC192 LR/STM64 LH 1550,<br>OC192 IR/STM64 1550, |  |  |  |  |

|                            |                                                                             |  |  |  |  |

|                            |                                                                             |  |  |  |  |

|                            | OC192 SR/STM64 SR 1310                                                      |  |  |  |  |

| BLSR Switch (Monitor Only) | OC12/STM4-4                                                                 |  |  |  |  |

|                            | OC48 IR/STM16 SH AS 1310,                                                   |  |  |  |  |

|                            | OC48 LR/STM16 LH AS 1550                                                    |  |  |  |  |

|                            | OC192 LR/STM64 LH 1550,                                                     |  |  |  |  |

|                            | OC192 IR/STM64 1550,                                                        |  |  |  |  |

|                            | OC192 SR/STM64 SR 1310                                                      |  |  |  |  |

# Path Signal Label, C2 Byte

One of the overhead bytes in the SONET frame is the C2 byte. The SONET standard defines the C2 byte as the path signal label. The purpose of this byte is to communicate the payload type being encapsulated by the STS path overhead (POH). The C2 byte functions similarly to EtherType and Logical Link Control (LLC)/Subnetwork Access Protocol (SNAP) header fields on an Ethernet network; it allows a single interface to transport multiple payload types simultaneously. C2 byte hex values supported by the ONS 15454 are provided in Table 2-10.

Table 2-10 C2 STS Path Signal Label Assignments for Signals

| Hex Code | Content of the STS Synchronous Payload Envelope (SPE)            |

|----------|------------------------------------------------------------------|

| 0x00     | Unequipped                                                       |

| 0x01     | Equipped - nonspecific payload                                   |

| 0x02     | VT structured STS-1 (DS-1)                                       |

| 0x03     | Locked VT mode                                                   |

| 0x04     | Asynchronous mapping for DS-3                                    |

| 0x12     | Asynchronous mapping for DS4NA                                   |

| 0x13     | Mapping for Asynchronous Transfer Mode (ATM)                     |

| 0x14     | Mapping for distributed queue dual bus (DQDB)                    |

| 0x15     | Asynchronous mapping for fiber distributed data interface (FDDI) |

| 0x16     | High level data link control (HDLC) over SONET mapping           |

| 0xFD     | Reserved                                                         |

| 0xFE     | 0.181 Test signal (TSS1 to TSS3) mapping SDH network             |

| 0xFF     | Alarm indication signal, path (AIS-P)                            |

If a circuit is provisioned using a terminating card, the terminating card provides the C2 byte. A VT circuit is terminated at the XCVT or XC10G card, which generates the C2 byte (0x02) downstream to the STS terminating cards. The XCVT or XC10G card generates the C2 value (0x02) to the DS1 or DS3XM terminating card. If an optical circuit is created with no terminating cards, the test equipment must supply the path overhead in terminating mode. If the test equipment is in pass-through mode, the C2 values usually change rapidly between 0x00 and 0xFF. Adding a terminating card to an optical circuit usually fixes a circuit having C2 byte problems. Table 2-11 lists label assignments for signals with payload defects.

Table 2-11 C2 STS Path Signal Label Assignments for Signals with Payload Defects

| Hex Code Content of the STS SPE |                                                                         |  |  |

|---------------------------------|-------------------------------------------------------------------------|--|--|

| 0xE1                            | VT-structured STS-1 SPE with 1 VTx payload defect (STS-1 with 1 VTx PD) |  |  |

| 0xE2                            | STS-1 with 2 VTx PDs                                                    |  |  |

| 0xE3                            | STS-1 with 3 VTx PDs                                                    |  |  |

| 0xE4                            | STS-1 with 4 VTx PDs                                                    |  |  |

| 0xE5                            | STS-1 with 5 VTx PDs                                                    |  |  |

| 0xE6                            | STS-1 with 6 VTx PDs                                                    |  |  |

Table 2-11 C2 STS Path Signal Label Assignments for Signals with Payload Defects (continued)

| Hex Code | Content of the STS SPE                                                                                                    |

|----------|---------------------------------------------------------------------------------------------------------------------------|

| 0xE7     | STS-1 with 7 VTx PDs                                                                                                      |

| 0xE8     | STS-1 with 8 VTx PDs                                                                                                      |

| 0xE9     | STS-1 with 9 VTx PDs                                                                                                      |

| 0xEA     | STS-1 with 10 VTx PDs                                                                                                     |

| 0xEB     | STS-1 with 11 VTx PDs                                                                                                     |

| 0xEC     | STS-1 with 12 VTx PDs                                                                                                     |

| 0xED     | STS-1 with 13 VTx PDs                                                                                                     |

| 0xEE     | STS-1 with 14 VTx PDs                                                                                                     |

| 0xEF     | STS-1 with 15 VTx PDs                                                                                                     |

| 0xF0     | STS-1 with 16 VTx PDs                                                                                                     |

| 0xF1     | STS-1 with 17 VTx PDs                                                                                                     |

| 0xF2     | STS-1 with 18 VTx PDs                                                                                                     |

| 0xF3     | STS-1 with 19 VTx PDs                                                                                                     |

| 0xF4     | STS-1 with 20 VTx PDs                                                                                                     |

| 0xF5     | STS-1 with 21 VTx PDs                                                                                                     |

| 0xF6     | STS-1 with 22 VTx PDs                                                                                                     |

| 0xF7     | STS-1 with 23 VTx PDs                                                                                                     |

| 0xF8     | STS-1 with 24 VTx PDs                                                                                                     |

| 0xF9     | STS-1 with 25 VTx PDs                                                                                                     |

| 0xFA     | STS-1 with 26 VTx PDs                                                                                                     |

| 0xFB     | STS-1 with 27 VTx PDs                                                                                                     |

| 0xFC     | VT-structured STS-1 SPE with 28 VT1.5 (Payload defects or a non-VT-structured STS-1 or STS-Nc SPE with a payload defect.) |

| 0xFF     | Reserved                                                                                                                  |

# **Payload Mapping**

The SONET and SDH payloads supported by the ONS 15454 are shown in Table 2-12.

Table 2-12 SONET and SDH Payloads Supported

| SONET    | SDH    |

|----------|--------|

| STS-1    | _      |

| STS-3C   | STM-1  |

| STS-12C  | STM-4  |

| STS-48C  | STM-16 |

| STS-192C | STM-64 |

The SONET payload mappings for each interface supported by the Cisco ONS 15454 are shown in Table 2-13.

Table 2-13 ONS 15454 SONET Payload Mappings

| ONS 15454 Card<br>Type | I/O Format                                                                              | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                                                                                                          | No. of<br>STSs |

|------------------------|-----------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| DS1-14                 | DS1                                                                                     | 14               | VT1.5 mapped in an STS                                                                                                                                                                                                                                                                          | 1              |

| DS1N-14                |                                                                                         |                  |                                                                                                                                                                                                                                                                                                 |                |

| DS3-12                 | Any type of DS3 mapping: M13, M23,                                                      | 12               | DS3 mapped in an STS                                                                                                                                                                                                                                                                            | 12             |

| DS3N-12                | clear channel, DS3 ATM, etc.                                                            |                  |                                                                                                                                                                                                                                                                                                 |                |

| DS3-12E                | Any type of DS3 mapping, plus J1 path                                                   | 12               | DS3 mapped in an STS                                                                                                                                                                                                                                                                            | 12             |

| DS3N-12E               | trace                                                                                   |                  |                                                                                                                                                                                                                                                                                                 |                |

| DS3/EC1-48             | Any type of DS3 mapping, plus J1 path trace <sup>1</sup> .                              | 48               | DS3 mapped in an STS.                                                                                                                                                                                                                                                                           | 48             |

| DS3XM-6                | M13 mapped DS3                                                                          | 6                | VT1.5 mapped in an STS                                                                                                                                                                                                                                                                          | 6              |

| DS3XM-12               | M13 mapped DS3                                                                          | 12               | DS3 or VT1.5 mapped in an STS-1                                                                                                                                                                                                                                                                 | 48             |

| EC1-12                 | DS3 mapped STS, VT1.5 mapped STS or clear channel STS (Electrical)                      | 12               | DS3, VT1.5 mapped in an STS or STS-1                                                                                                                                                                                                                                                            | 12             |

| All OC3 Cards          | Any type of DS3 mapped STS, VT1.5 mapped STS, clear channel STS or OC-Nc ATM (Optical). | 4 or 8           | This card's mapping can be a DS3 mapped STS or a VT1.5 mapped STS. However, it does not convert between the two different mappings.                                                                                                                                                             | 12 or<br>24    |

|                        |                                                                                         |                  | Mapping can also be STS-N or STS-Nc. Each of the STS streams can be configured to any combination of STS-1 or STS-3c, provided the sum of the circuit sizes that terminate on a card do not exceed STS-12c for the 4-port OC3 card or 24c for the 8-port card.                                  |                |

| All OC12 Cards         | Any type of DS3 mapped STS, VT1.5 mapped STS, clear channel STS or OC-Nc ATM (Optical). | 1 or 4           | This card's mapping can be a DS3 mapped STS or a VT1.5 mapped STS. However, it does not convert between the two different mappings.                                                                                                                                                             | 12 or<br>48    |

|                        |                                                                                         |                  | Mapping can also be STS-N or STS-Nc. Each of the STS streams can be configured to any combination of STS-1, STS-3c, STS-6c, STS-9c, and STS-12c, provided the sum of the circuit sizes that terminate on a card do not exceed STS-12c for the single port OC12 card or 48c for the 4-port card. |                |

Table 2-13 ONS 15454 SONET Payload Mappings (continued)

| ONS 15454 Card<br>Type | I/O Format                                                                              | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                                                                                                                                                       | No. of<br>STSs |

|------------------------|-----------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| All OC48 Cards         | Any type of DS3 mapped STS, VT1.5 mapped STS, clear channel STS or OC-Nc ATM (Optical). | 1                | This card's mapping can be a DS3 mapped STS or a VT1.5 mapped STS. However, it does not convert between the two different mappings.                                                                                                                                                                                                          | 48             |

|                        |                                                                                         |                  | Mapping can also be STS-N or STSNc. Each of the STS streams can be configured to any combination of STS-1, STS-3c, STS-6c, STS-9c, STS-12c, STS-24c, and STS-48c circuit sizes, provided the sum of the circuit sizes that terminate on a card do not exceed STS-48c.                                                                        |                |

| All OC192 Cards        | Any type of DS3 mapped STS, VT1.5 mapped STS, clear channel STS or OC-Nc ATM (Optical). | 1                | This card's mapping can be a DS3 mapped STS or a VT1.5 mapped STS. However, it does not convert between the two different mappings.                                                                                                                                                                                                          | 192            |

|                        |                                                                                         |                  | Mapping can also be STS-N or STSNc. Each of the STS streams can be configured to any combination of STS-1, STS-3c, STS-6c, STS-9c, STS-12c, STS-24c, STS-48c, and STS-192c circuit sizes, provided the sum of the circuit sizes that terminate on a card do not exceed STS-192c.                                                             |                |

| CE-100T-8              | Ethernet (Electrical)                                                                   | 8                | 10/100 Mb/s                                                                                                                                                                                                                                                                                                                                  | 12             |

|                        |                                                                                         |                  | Ethernet traffic in HDLC, mapped into STS-12 payloads, making use of low order (VT1.5) virtual concatenation, high order (STS-1) virtual concatenation, and generic framing procedure (GFP), point-to-point protocol/high-level data link control (PPP/HDLC) framing protocols. It also supports the link capacity adjustment scheme (LCAS). |                |

| E100T                  | Ethernet (Electrical)                                                                   | 12               | 10/100 Mb/s Ethernet traffic in HDLC,                                                                                                                                                                                                                                                                                                        | 12             |

| E100T-G                |                                                                                         |                  | mapped in an STS-Nc.                                                                                                                                                                                                                                                                                                                         |                |

| E1000-2                | Ethernet (Electrical)                                                                   | 2                | 1000 Mb/s Ethernet traffic in HDLC,                                                                                                                                                                                                                                                                                                          | 12             |

| E1000-G                |                                                                                         |                  | mapped in an STS-Nc.                                                                                                                                                                                                                                                                                                                         |                |

Table 2-13 ONS 15454 SONET Payload Mappings (continued)

| ONS 15454 Card<br>Type | I/O Format                                  | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                                                                                                                                     | No. of<br>STSs |

|------------------------|---------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| G1000-4<br>G1K-4       | Ethernet (Optical)                          | 4                | 1000 Mb/s Ethernet traffic in HDLC, mapped in an STS-Nc. You can map the 4 ports on the G1000-4 independently to any combination of STS-1, STS-3c, STS-6c, STS-9c, STS-12c, STS-24c, and STS-48c circuit sizes, provided the sum of the circuit sizes that terminate on a card do not exceed STS-48c.                      | 48             |

|                        |                                             |                  | To support a gigabit Ethernet port at full line rate, an STS circuit with a capacity greater or equal to 1Gb/s (bi-directional 2 Gb/s) is needed. An STS-24c is the minimum circuit size that can support a gigabit Ethernet port at full line rate. The G1000-4 supports a maximum of two ports at full line rate.        |                |

| ML100T-12              | Ethernet (Optical)  Layer 2/Layer 3 Routing | 12               | Ethernet in HDLC, mapped in an STS-Nc. You can map the 2 ports on the ML-series cards independently to any combination of STS-1, STS-3c, STS-6c, STS-9c, STS-12c, and STS-24c circuit sizes, provided the sum of the circuit sizes that terminate on a card do not exceed STS-48c. Up to 2 STS-24c circuits are supported. | 48             |

| ML1000-2               | Ethernet (Optical) Layer 2/Layer 3 Routing  | 2                | 1000 Mb/s Ethernet traffic in HDLC, mapped in an STS-Nc. You can map the 2 ports on the ML-series cards independently to any combination of STS-1, STS-3c, STS-6c, STS-9c, STS-12c, and STS-24c circuit sizes, provided the sum of the circuit sizes that terminate on a card do not exceed STS-48c.                       | 48             |

|                        |                                             |                  | To support a gigabit Ethernet port at full line rate, an STS circuit with a capacity greater or equal to 1Gb/s (bi-directional 2 Gb/s) is needed. An STS-24c is the minimum circuit size that can support a gigabit Ethernet port at full line rate. Up to 2 STS-24c circuits are supported.                               |                |

Table 2-13 ONS 15454 SONET Payload Mappings (continued)

| ONS 15454 Card<br>Type | I/O Format                                                                                                                                         | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                                                                                                                                                | No. of<br>STSs |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| FC_MR-4                | Fibre Channel/ Fiber Connectivity (FICON)                                                                                                          | 4                | This card transports non-SONET-framed, block-coded protocols over SONET in virtually or contiguously concatenated payloads. The FC_MR-4 can transport Fibre Channel over SONET using Fibre-Channel client interfaces and allows transport of up to two STS-24c/VC4-8c or one STS-48c/VC4-16c, or two VCAT circuits (STC3c-8V/VC4-8v). | 48             |

| OSCM                   | The OSCM has one set of optical ports and one Ethernet port.                                                                                       | 2                | OC-3/STM-1 formatted OSC.                                                                                                                                                                                                                                                                                                             | 3              |

| OSC-CSM                | The OSC-CSM has three sets of optical ports and one Ethernet port.                                                                                 | 4                | OC-3/STM-1 formatted OSC.                                                                                                                                                                                                                                                                                                             | 3              |

| OPT-PRE                | The OPT-PRE amplifier card is designed to support 64 channels at 50-GHz channel spacing, but currently limited to 32 channels at 100 GHz.          | 5                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

| OPT-BST                | The OPT-BST amplifier card is designed to support 64 channels at 50-GHz channel spacing, but currently limited to 32 channels at 100 GHz.          | 4                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

| 32MUX-O                | The 32-Channel Multiplexer (32MUX-O) card multiplexes 32 100-GHz-spaced channels identified in the channel plan.                                   | 5                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

| 32DMX-O                | The 32-Channel Demultiplexer (32DMX-O) card demultiplexes 32 100-GHz-spaced channels identified in the channel plan.                               | 5                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

| 32DMX                  | The card receives an aggregate optical signal on its COM RX port and demultiplexes it into to 32 100-GHz-spaced channels.                          | 5                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

| 32WSS                  | The 32-Channel Wavelength Selective Switch (32WSS) card performs channel add/drop processing within the ONS 15454 DWDM node.                       | 7                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

| 4MD-xx.x               | The 4-Channel Multiplexer/Demultiplexer (4MD-xx.x) card multiplexes and demultiplexes four 100-GHz-spaced channels identified in the channel plan. | 5                | C-band DWDM OC-N.                                                                                                                                                                                                                                                                                                                     | 192            |

Table 2-13 ONS 15454 SONET Payload Mappings (continued)

| ONS 15454 Card<br>Type | I/O Format                                                                                                                                       | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                         | No. of<br>STSs |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| AD-1C-xx.x             | The 1-Channel OADM (AD-1C-xx.x) card passively adds or drops one of the 32 channels utilized within the 100-GHz-spacing of the DWDM card system. | 3                | C-band DWDM OC-N.                                                                                                                                                                                              | 192            |

| AD-2C-xx.x             | The 2-Channel OADM (AD-2C-xx.x) card passively adds or drops two adjacent 100-GHz channels within the same band.                                 | 4                | C-band DWDM OC-N.                                                                                                                                                                                              | 192            |

| AD-4C-xx.x             | The 4-Channel OADM (AD-4C-xx.x) card passively adds or drops all four 100-GHz-spaced channels within the same band.                              | 6                | C-band DWDM OC-N.                                                                                                                                                                                              | 192            |

| AD-1B-xx.x             | The 1-Band OADM (AD-1B-xx.x) card passively adds or drops a single band of four adjacent 100-GHz-spaced channels.                                | 3                | C-band DWDM OC-N.                                                                                                                                                                                              | 192            |

| AD-4B-xx.x             | The 4-Band OADM (AD-4B-xx.x) card passively adds or drops four bands of four adjacent 100-GHz-spaced channels.                                   | 6                | C-band DWDM OC-N.                                                                                                                                                                                              | 192            |

| MXP_2.5G_10G           | 2.5 Gb/s signals                                                                                                                                 | 4/1              | This card multiplexes/ demultiplexes four 2.5 Gb/s signals (client side) into one 10-Gbps, 100-GHz DWDM signal (trunk side). It provides one extended long-range STM-64/OC-192 port per card on the trunk side | 192            |

| MXP_2.5G_10E           | Four 2.5 Gb/s client interfaces (OC-48/STM-16) and one 10 Gb/s trunk.                                                                            | 9                | The four OC-48 signals are mapped into a ITU-T G.709 OTU2 signal using standard ITU-T G.709 multiplexing.                                                                                                      | 192            |

Table 2-13 ONS 15454 SONET Payload Mappings (continued)

| ONS 15454 Card<br>Type       | I/O Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | No. of<br>STSs |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| MXP_MR_2.5G and MXPP_MR_2.5G | The 2.5-Gb/s Multirate Muxponder-100 GHz-Tunable 15xx.xx-15yy.yy (MXP_MR_2.5G) card aggregates a mix and match of client Storage Area Network (SAN) service client inputs (GE, FICON, and Fibre Channel) into one 2.5 Gb/s STM-16/OC-48 DWDM signal on the trunk side. It provides one long-reach STM-16/OC-48 port per card and is compliant with Telcordia GR-253-CORE.  The 2.5-Gb/s Multirate Muxponder-Protected-100GHz - Tunable 15xx.xx-15yy.yy (MXPP_MR_2.5G) card aggregates various client SAN service client inputs (GE, FICON, and Fibre Channel) into one 2.5 Gb/s STM-16/OC-48 DWDM signal on the trunk side. It provides two long-reach STM-16/OC-48 ports per card and is compliant with ITU-T G.957 and Telcordia GR-253-CORE. | 9/10             | The client interface supports the following payload types.  GE  1G FC  1G FC  1G FICON  2G FICON  All of the client interfaces supported use the Transparent Generic Framing Procedure (GFP-T) encapsulation method. The current version of the GFP-T, G.7041, supports transparent mapping of 8B/10B block-coded protocols, including Gigabit Ethernet, Fibre Channel, and FICON.  In addition to the GFP mapping, 1 Gb/s traffic on port 1 or port 2 of the high-speed SERDES is mapped to an STS-24c channel. If two 1 Gb/s client signals are present at port 1 and port 2 of the high-speed SERDES, the port 1 signal is mapped into the first STS-24c channel and the port 2 signal into the second STS-24c channel. The two channels are then mapped into an OC-48 trunk channel.  Only Contiguous concatenation is supported for the MXP_MR_2.5G and MXPP_MR_2.5G (no VCAT). Port one supports:  1GE and 1G-FC mapped over first STS-24c payload  2G-FC mapped over STS-48c  Port two supports:  1GE and 1G-FC mapped over second STS-24c payload. | 48             |

Table 2-13 ONS 15454 SONET Payload Mappings (continued)

| ONS 15454 Card<br>Type             | I/O Format                                                                                                                                                                                                                                                                                                                                                                   | No. of I/O Ports | Internal SONET Mapping                                                                                                                                                                                                                                                                                                                                           | No. of<br>STSs |

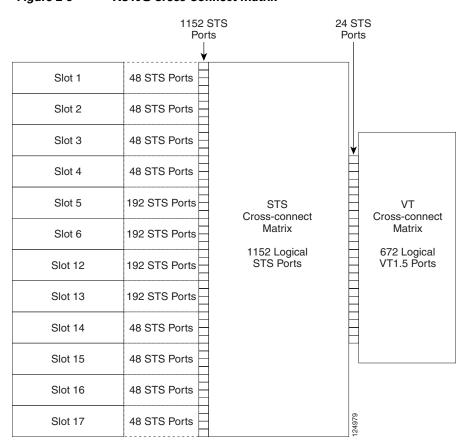

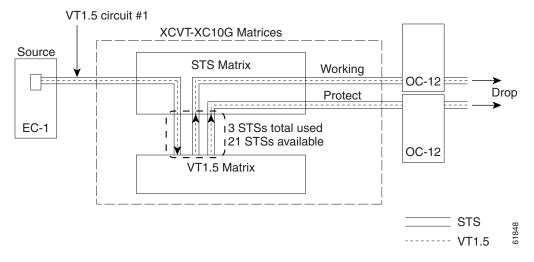

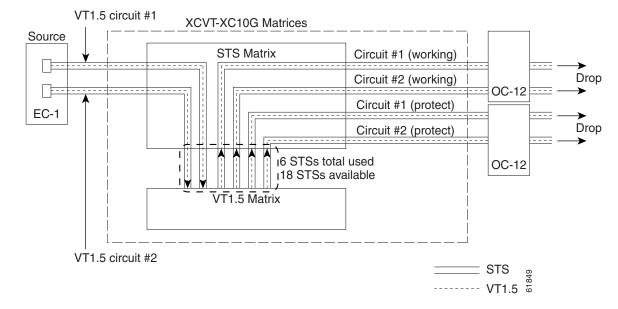

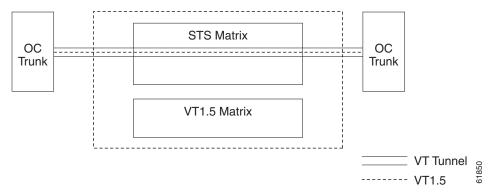

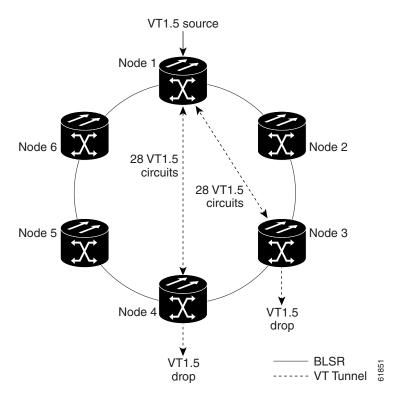

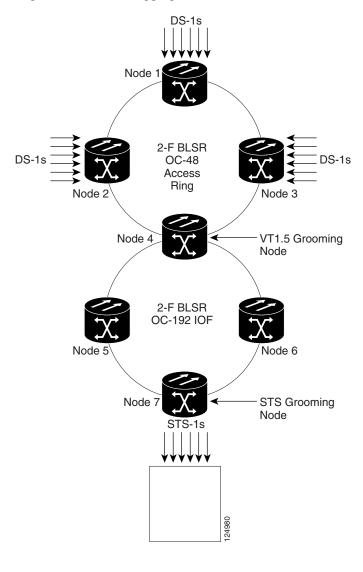

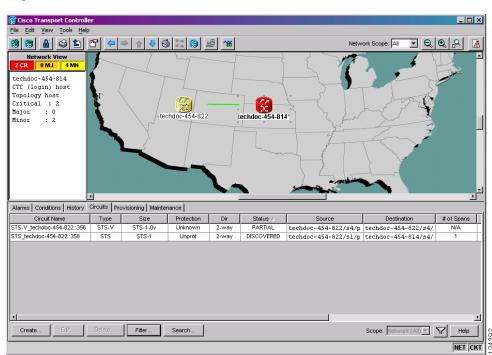

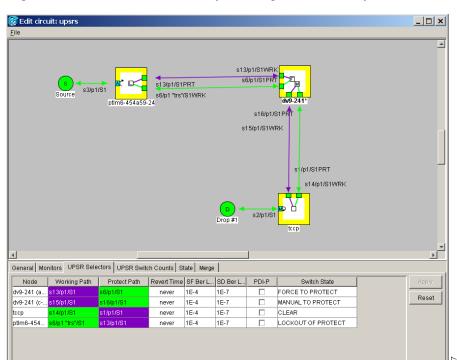

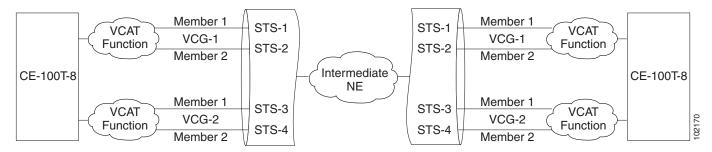

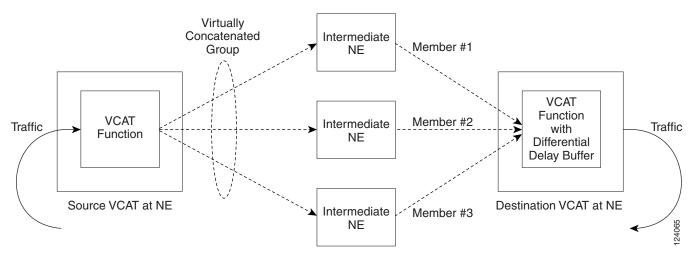

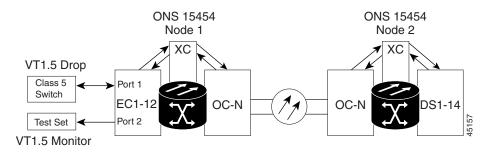

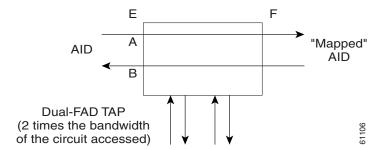

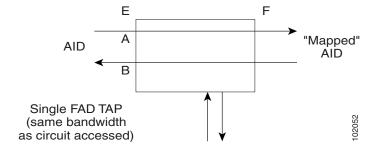

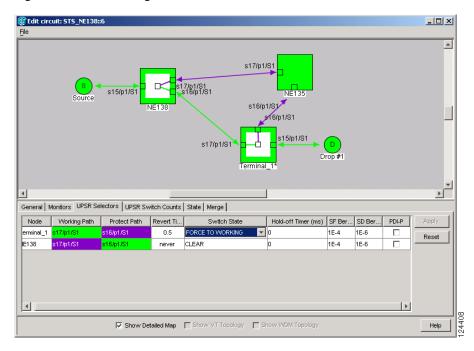

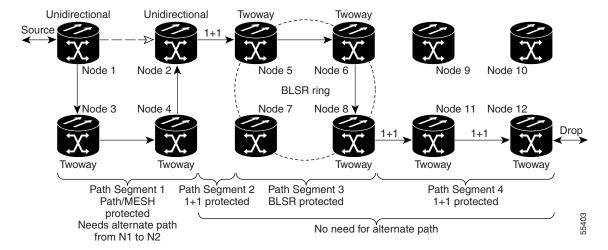

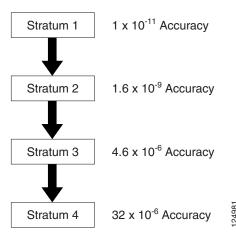

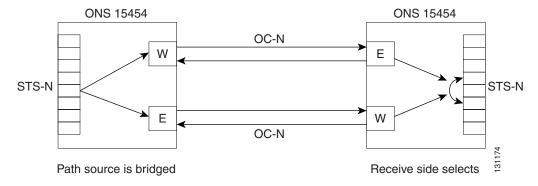

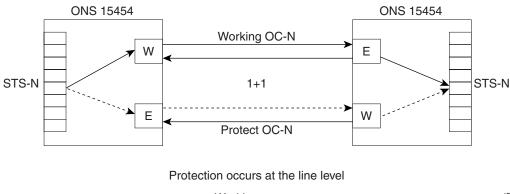

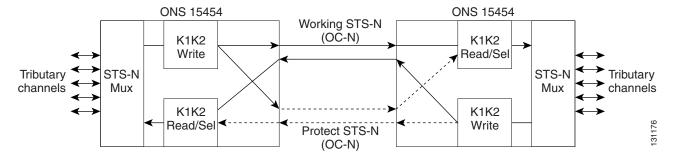

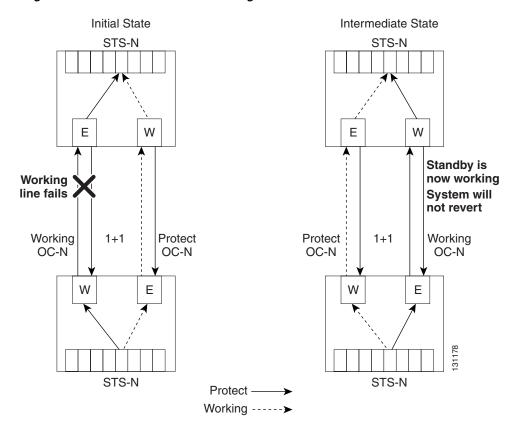

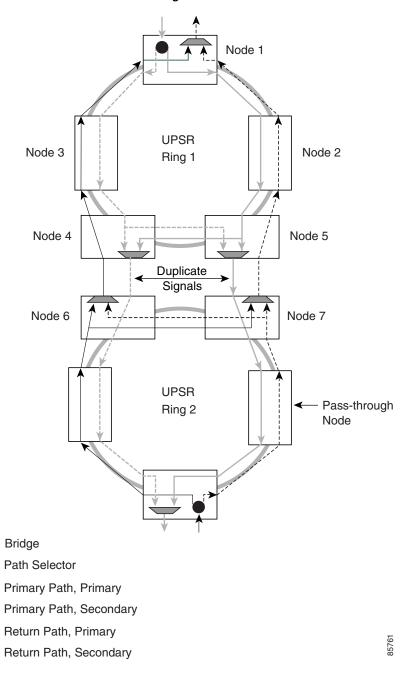

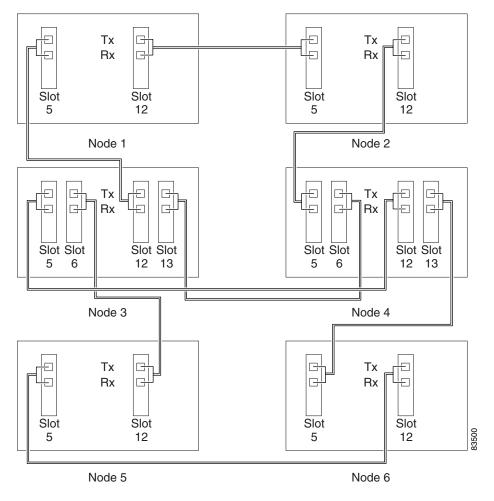

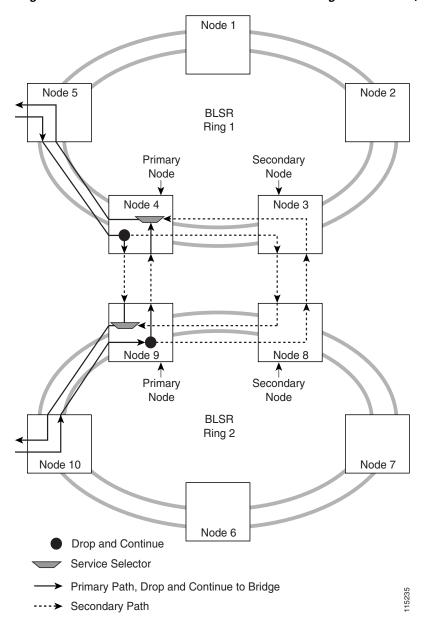

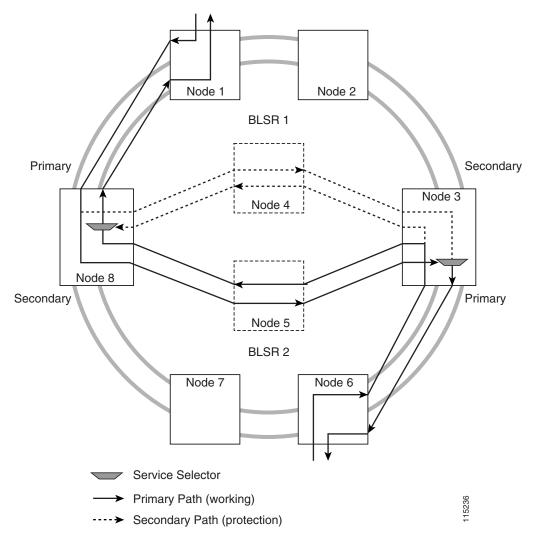

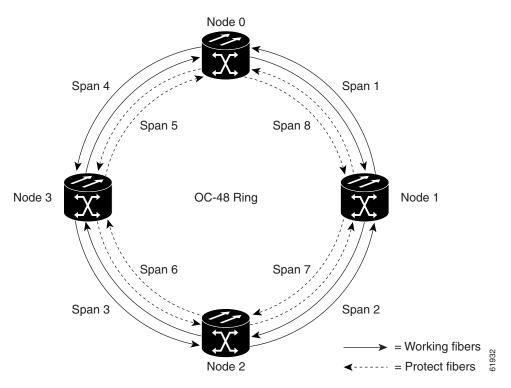

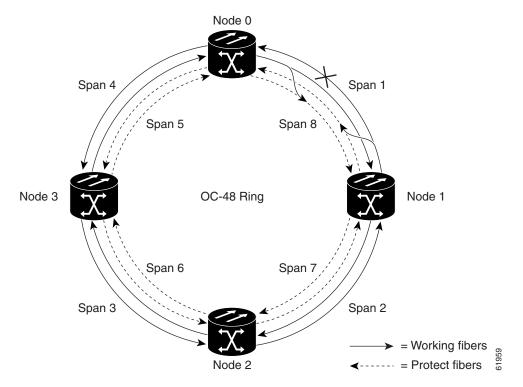

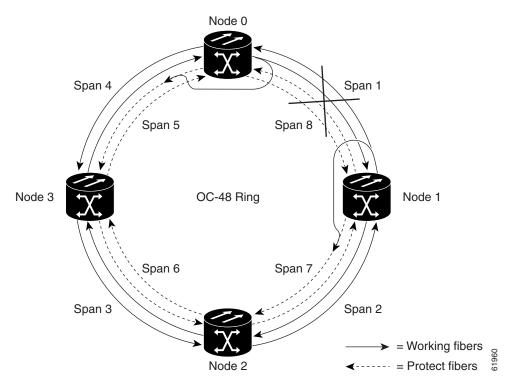

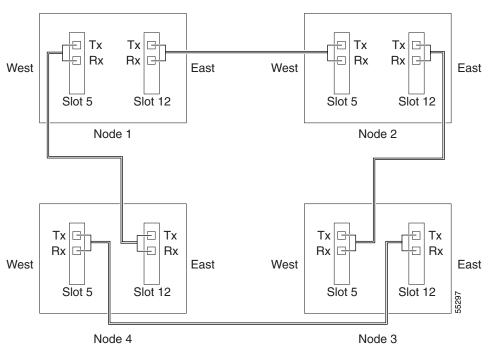

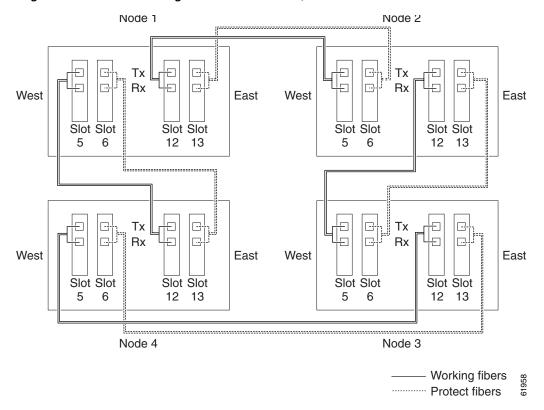

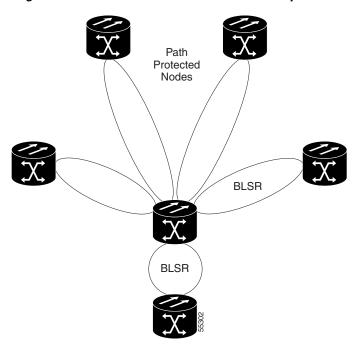

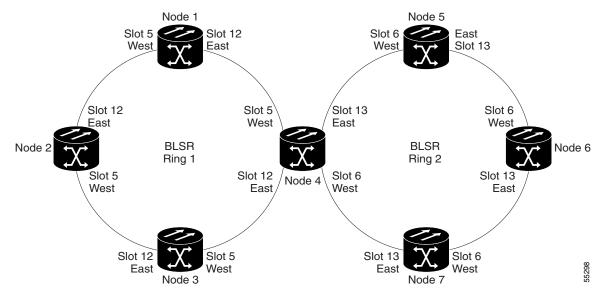

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|